# APM32F103xC

**Errata Sheet**

Version: V 2.0

### **Contents**

| 1 Introduction                                          |    |  |  |

|---------------------------------------------------------|----|--|--|

| 2 Product Version and Silk Screen Printing Instructions | 3  |  |  |

| 3 Errata List                                           | 4  |  |  |

| 4 GPIO                                                  | 5  |  |  |

| 4.1 GPIO output                                         | 5  |  |  |

| 5 System                                                | 6  |  |  |

| 5.1 PWR sleep mode                                      | 6  |  |  |

| 6 Clock                                                 | 7  |  |  |

| 6.1 HSE serves as the clock source                      |    |  |  |

| 7 USBD/CAN                                              | 8  |  |  |

| 7.1 Combined use of USBD/CAN7.2 CAN2_IO remapping       |    |  |  |

| 8 SPI                                                   | 9  |  |  |

| 8.1 Module timing of SPI                                | 9  |  |  |

| 9 Flash                                                 | 10 |  |  |

| 9.1 Low-power wake-up9.2 Flash erase                    |    |  |  |

| 10 Revision history                                     | 12 |  |  |

### 1 Introduction

This Manual mainly introduces the limitations of the APM32F103xC series products during use. If you encounter the application scenarios described in the manual during the use of the product, please use the product according to the solutions provided in the manual; if no solution is provided, please avoid this application scenario.

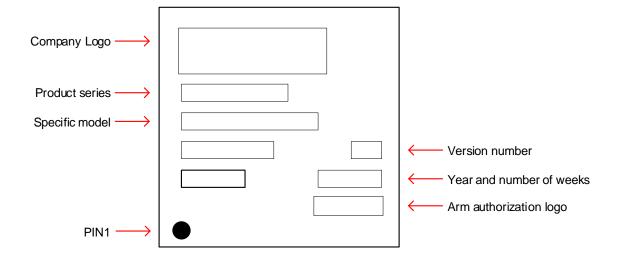

# 2 Product Version and Silk Screen Printing Instructions

Figure 1 Product Version and Silk Screen Printing Instructions

### 3 Errata List

Table 1 Errata List

| Cataman   | Introduction                   | Product | Product version |  |

|-----------|--------------------------------|---------|-----------------|--|

| Category  |                                | A1      | A2              |  |

| GPIO      | GPIO output                    | •       | •               |  |

|           | AC characteristics of IO port  | •       | •               |  |

|           | USART3 and FSMC remapping      | •       | •               |  |

| System    | PWR sleep mode                 | •       | •               |  |

| Clock     | HSE serves as the clock source | •       | •               |  |

|           | PLL frequency multiplication   | •       | •               |  |

| LICDD/CAN | Combined use of USBD/CAN       | •       | •               |  |

| USBD/CAN  | CAN2_IO remapping              | •       | •               |  |

| SPI       | Module timing of SPI           | •       | •               |  |

| Floob     | Low-power wake-up              | •       | •               |  |

| Flash     | Flash erase                    | •       | •               |  |

Note: "•" indicates that this errata description is involved in this version; the 'X' indicates that it is not involved in this version.

### 4 GPIO

### 4.1 GPIO output

### **Problem description**

When the GPIO port is configured as multiplexing push-pull output, the output voltage may be affected by external interference and is unable to output accurate levels; when configured as floating input to read the external I/O input values, it may be affected by external interference and is unable to read accurate values.

#### **Solutions**

When configured as multiplexing push-pull output, connect an external pull-up resistor; when configured as floating input, connect an internal pull-up resistor externally or configure it as a pull-up input.

### 4.2 AC characteristics of IO port

### **Problem description**

AC characteristics of GPIO\_IO: PA8 and PC8 are equipped with an external 50pF load capacitor. At 2V low voltage, the output rate is 10MHz square wave, and the output duty cycle is high, ranging from 60% to 70%.

### **Solutions**

It is recommended to avoid the simultaneous occurrence of low-voltage and low-speed (2V, 10MHz) conditions when this pin is used.

The I/O speed is related to the configuration, normal at high speed and abnormal at low speed. For example, if I/O is configured to 50MHz mode and outputs 10M at 2V, the duty cycle is normal.

### 4.3 USART3 and FSMC remapping

### **Problem description**

USART\_USART3 remapping PD8 and PD9 pins conflicts with FSMC clock. Specifically: when remapping PD8 and PD9 as serial pins, enable FSMC clock but the serial communication cannot be used normally.

#### **Solutions**

Choose either of the following solutions:

- Use partial remapping function or default configuration of USART3.

- When USART3 TX is remapped to PD8 as a serial port pin, disable the SMC function.

### 5 System

### 5.1 PWR sleep mode

### **Problem description**

The PWR sleep mode\_WEF() instruction is invalid and cannot enter the low-power mode.

### **Solutions**

Choose either of the following solutions:

- It can be executed normally after it is reset through the reset pin.

- Set in the download of Keil (set the reset and run)

- Add the second WFE instruction and it can be executed normally.

- Modify the program, and use 1 WFI rather than WFE.

### 6 Clock

### 6.1 HSE serves as the clock source

### **Problem description**

When the timeout value of the software that sets the HSE startup time is too small (e.g. 0x0500), external clock startup ready timeout may occur, which may result in the failure of using HSE as the clock source.

#### **Solutions**

To ensure normal startup of the crystal oscillator, it is recommended to modify the external clock wait time timeout value to at least 0x3200.

The specific operation is modifying the macro definition of HSE\_STARTUP\_TIMEOUT. Macro definition varies depending on the version of the library function:

- For the V3.x version library functions, the macro definition is in XXX32F10x.h;

- For the library before V3.0, the macro definition is in XXX32f10x RCC.c.

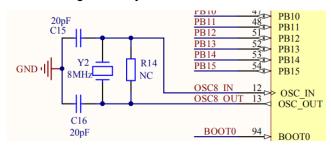

The recommended crystal oscillator circuit is shown below (the capacitance value should match the crystal oscillator model):

#define HSE\_STARTUP\_TIMEOUT ((uint16\_t)0x3200) (recommended 0x3200, maximum 0xffff).

Figure 2 Crystal Oscillator Circuit

### 6.2 PLL frequency multiplication

#### **Problem description**

After doubling to 24MHz using PLL, the frequency output through the PA8 pin is unstable.

#### **Solutions**

When using PLL multiplication, first use a large multiplication coefficient to increase the frequency of the VCO, and then output at a lower frequency. For example, increase the PLL frequency to 48MHz and then divide its frequency to 24MHz through an AHB prescaler.

### 7 USBD/CAN

### 7.1 Combined use of USBD/CAN

### **Problem description**

USBD1 and CAN2 of APM32F103xC can be used simultaneously, USBD2 and CAN1 can be used simultaneously, USBD1 and USBD2 cannot be used simultaneously, and CAN1 and CAN2 can be used simultaneously.

### **Solutions**

Use according to the recommendations of Datasheet and User Manual.

### 7.2 CAN2\_IO remapping

### **Problem description**

When multiple groups of peripheral I/O remap the configuration, if CAN2 remaps the configuration first and then other peripherals remap the configuration, CAN2 will fail to remap.

### **Solutions**

Put the CAN2 remapping operation behind the remapping operation of other peripherals.

### 8 SPI

### 8.1 Module timing of SPI

### **Problem description**

When SPI (SPI\_cmd() function ENABLE) is enabled, after SPI parameters are modified, the timing transmission of SPI for one byte is 16 clocks (normally 8 clocks).

### **Solutions**

The initialization standard operation of SPI is specifically:

Initialize the corresponding SCK MOSI, MISO and NSS, and enable SPI. To modify the parameters, first enable SPI (SPI\_cmd() function DISABLE) and then modify the corresponding configuration.

### 9 Flash

### 9.1 Low-power wake-up

### **Problem description**

The low-power and AHB frequency division scenario may result in abnormal clearing of the dcode buffer, thus entering hardfault.

#### **Solutions**

For the WFI and WFE low-power wake-up scenarios:

- For the WFI low-power wake-up scenarios, AHB should not divide the frequency (i.e.

ensure that the first interrupt vector data is read and returned from Flash, rather than

returned from buf). After the low power is awakened, enter the interrupt service function,

first read an address from each Flash bank in the interrupt service function and then start to

execute the real user program.

- For the WFI low-power wake-up scenarios, AHB should not divide the frequency (i.e.

ensure that the first interrupt vector data is read and returned from Flash, rather than

returned from buf). After the low power is awakened, start sequential execution, first read

an address from each bank and then start to execute the real user program.

#### 9.2 Flash erase

### **Problem description**

The erase operation and read Flash operation are performed concurrently, and a read Flash data error occurs when the erase operation is completed:

- The program executes FLASH->SR status register in sequence, and read errors may occur.

- In the process of erasing Flash, an interrupt occurs, and the interrupt service function contains a program of reading data from Flash, and data errors may occur when erasing is completed, and thus causes program exceptions.

### Solutions

Choose either of the following solutions:

- For regular erase scenarios (program sequential execution), after initiating erase, before executing FIASH\_GetBank1Status, add:

while (FLASH->SR&FLASH\_FLAG\_BANK1\_BSY)==FLASH\_FLAG\_BSY;

- For regular erase scenarios (program sequential execution), after the state is read for the first time, it will be executed once again before the total state returns:

${\sf FLASH\_GetBank1Status} \ {\sf sub-function}$

And AHB keeps the frequency not divided.

And AHB keeps the frequency not divided.

- For the interrupt scenarios, before erasing Flash, shield the interrupt, there will be no scenarios of entering the interrupt in the erasing process, and it will change to the regular erase scenario.

- For the interrupt scenarios, add a statement of waiting for the Flash erase operation to end at the beginning of the interrupt service function:

while (FLASH->SR&FLASH\_FLAG\_BANK1\_BSY)==FLASH\_FLAG\_BSY;

Wait for the Flash erase operation to end, then execute the interrupt service program, and keep the AHB frequency not divided.

# 10 Revision history

### Table2 Document Revision History

| Date        | Version | Revision History |

|-------------|---------|------------------|

| August 2024 | 1.0     | New edition      |

## **Statement**

This document is formulated and published by Geehy Semiconductor Co., Ltd. (hereinafter referred to as "Geehy"). The contents in this document are protected by laws and regulations of trademark, copyright and software copyright. Geehy reserves the right to make corrections and modifications to this document at any time. Read this document carefully before using Geehy products. Once you use the Geehy product, it means that you (hereinafter referred to as the "users") have known and accepted all the contents of this document. Users shall use the Geehy product in accordance with relevant laws and regulations and the requirements of this document.

#### 1. Ownership

This document can only be used in connection with the corresponding chip products or software products provided by Geehy. Without the prior permission of Geehy, no unit or individual may copy, transcribe, modify, edit or disseminate all or part of the contents of this document for any reason or in any form.

The "极海" or "Geehy" words or graphics with "®" or "TM" in this document are trademarks of Geehy. Other product or service names displayed on Geehy products are the property of their respective owners.

### 2. No Intellectual Property License

Geehy owns all rights, ownership and intellectual property rights involved in this document.

Geehy shall not be deemed to grant the license or right of any intellectual property to users explicitly or implicitly due to the sale or distribution of Geehy products or this document.

If any third party's products, services or intellectual property are involved in this document, it shall not be deemed that Geehy authorizes users to use the aforesaid third party's products, services or intellectual property. Any information regarding the application of the product, Geehy hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party, unless otherwise agreed in sales order or sales contract.

#### 3. Version Update

Users can obtain the latest document of the corresponding models when ordering Geehy products.

If the contents in this document are inconsistent with Geehy products, the agreement in the sales order or the sales contract shall prevail.

### 4. Information Reliability

The relevant data in this document are obtained from batch test by Geehy Laboratory or cooperative third-party testing organization. However, clerical errors in correction or errors caused by differences in testing environment may occur inevitably. Therefore, users should understand that Geehy does not bear any responsibility for such errors that may occur in this document. The relevant data in this document are only used to guide users as performance parameter reference and do not constitute Geehy's guarantee for any product performance.

Users shall select appropriate Geehy products according to their own needs, and effectively verify and test the applicability of Geehy products to confirm that Geehy products meet their own needs, corresponding standards, safety or other reliability requirements. If losses are caused to users due to user's failure to fully verify and test Geehy products, Geehy will not bear any responsibility.

### 5. Legality

USERS SHALL ABIDE BY ALL APPLICABLE LOCAL LAWS AND REGULATIONS WHEN USING THIS DOCUMENT AND THE MATCHING GEEHY PRODUCTS. USERS SHALL UNDERSTAND THAT THE PRODUCTS MAY BE RESTRICTED BY THE EXPORT, RE-EXPORT OR OTHER LAWS OF THE COUNTRIES OF THE PRODUCTS SUPPLIERS, GEEHY, GEEHY DISTRIBUTORS AND USERS. USERS (ON BEHALF OR ITSELF, SUBSIDIARIES AND AFFILIATED ENTERPRISES) SHALL AGREE AND PROMISE TO ABIDE BY ALL APPLICABLE LAWS AND REGULATIONS ON THE EXPORT AND RE-EXPORT OF GEEHY PRODUCTS AND/OR TECHNOLOGIES AND DIRECT PRODUCTS.

### 6. Disclaimer of Warranty

THIS DOCUMENT IS PROVIDED BY GEEHY "AS IS" AND THERE IS NO WARRANTY OF ANY KIND, EITHER EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, TO THE EXTENT PERMITTED BY APPLICABLE LAW.

GEEHY'S PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED FOR USE AS CRITICAL COMPONENTS IN MILITARY, LIFE-SUPPORT, POLLUTION CONTROL, OR HAZARDOUS SUBSTANCES MANAGEMENT SYSTEMS, NOR WHERE FAILURE COULD RESULT IN INJURY, DEATH, PROPERTY OR ENVIRONMENTAL DAMAGE.

IF THE PRODUCT IS NOT LABELED AS "AUTOMOTIVE GRADE," IT SHOULD NOT BE CONSIDERED SUITABLE FOR AUTOMOTIVE APPLICATIONS. GEEHY ASSUMES NO LIABILITY FOR THE USE BEYOND ITS SPECIFICATIONS OR GUIDELINES.

THE USER SHOULD ENSURE THAT THE APPLICATION OF THE PRODUCTS COMPLIES

WITH ALL RELEVANT STANDARDS, INCLUDING BUT NOT LIMITED TO SAFETY, INFORMATION SECURITY, AND ENVIRONMENTAL REQUIREMENTS. THE USER ASSUMES FULL RESPONSIBILITY FOR THE SELECTION AND USE OF GEEHY PRODUCTS. GEEHY WILL BEAR NO RESPONSIBILITY FOR ANY DISPUTES ARISING FROM THE SUBSEQUENT DESIGN OR USE BY USERS.

### 7. Limitation of Liability

IN NO EVENT, UNLESS REQUIRED BY APPLICABLE LAW OR AGREED TO IN WRITING WILL GEEHY OR ANY OTHER PARTY WHO PROVIDES THE DOCUMENT AND PRODUCTS "AS IS", BE LIABLE FOR DAMAGES, INCLUDING ANY GENERAL, SPECIAL, DIRECT, INCIDENTAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE USE OR INABILITY TO USE THE DOCUMENT AND PRODUCTS (INCLUDING BUT NOT LIMITED TO LOSSES OF DATA OR DATA BEING RENDERED INACCURATE OR LOSSES SUSTAINED BY USERS OR THIRD PARTIES). THIS COVERS POTENTIAL DAMAGES TO PERSONAL SAFETY, PROPERTY, OR THE ENVIRONMENT, FOR WHICH GEEHY WILL NOT BE RESPONSIBLE.

### 8. Scope of Application

The information in this document replaces the information provided in all previous versions of the document.

© 2024 Geehy Semiconductor Co., Ltd. - All Rights Reserved